The Center for Intelligent Systems (CIS), established in 1989, is a multidisciplinary research center which aims to conduct theoretical and applied research in various aspects of autonomous systems, machine learning and computer vision. The center encourages interdisciplinary interaction and promotes collaboration with numerous peers active in our field of interests.

Currently the center includes four laboratories: MARS, VISTA, ISL and CRL.

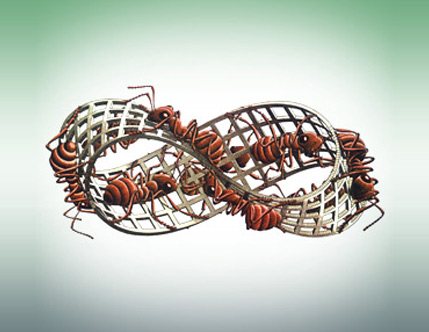

The MARS Laboratory is dedicated to research on Swarm, or Multi-agent, or Ant Robotics. Our inspiration comes from biology, from the wonders of ant colonies, or from other social insects and animals.

As such, we usually deal with very simple robotic agents, having restricted sensing and communication capabilities, and analyze, both mathematically and experimentally, via simulations and hardware implementations, the capabilities of such systems to organize themselves into formations, to patrol and cover a region in their environment, or to achieve other interesting collaborative tasks.

The VISTA laboratory was founded in 2017 and focuses on theoretical and practical aspects of machine vision and learning.

Our research avenues include computational methods in imaging and 3D sensing, image processing, computer vision, numerical geometry, machine learning, and large-scale data analysis and their real-world applications.

The main mission of CLAIR Lab is to investigate collaboration in multi-agent AI systems and to develop theoretical foundations for using AI to design AI systems that support effective and sustainable collaborations between automated agents and between automated agents and people.

To support our theoretical work and ground it in practical settings, we aim to evaluate our developed frameworks on a variety of multi-agent systems, including both virtual and robotic multi-agent systems.

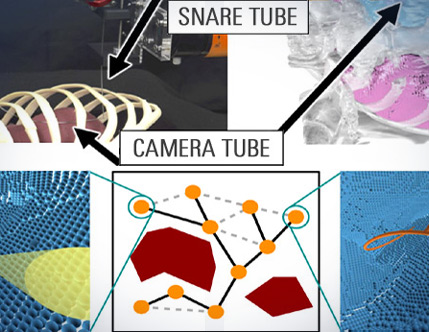

The Computational Robotics Lab is a center for foundational research on the computational challenges that arise when planning for robots.

We focus primarily on complex robotic systems such as those that arise in medical applications and warehouse domains.

The Intelligent Systems Laboratory’s (ISL) scope of activities focused on Computer Vision, Robotics, Learning methodologies, and Autonomous systems.

Research projects include advanced undergraduate term and year projects, M.Sc. and Ph.D. theses.

Active and successful collaboration with the industry takes place as well, and several PhD level researchers from other universities and from the industry collaborate with the ISL members.